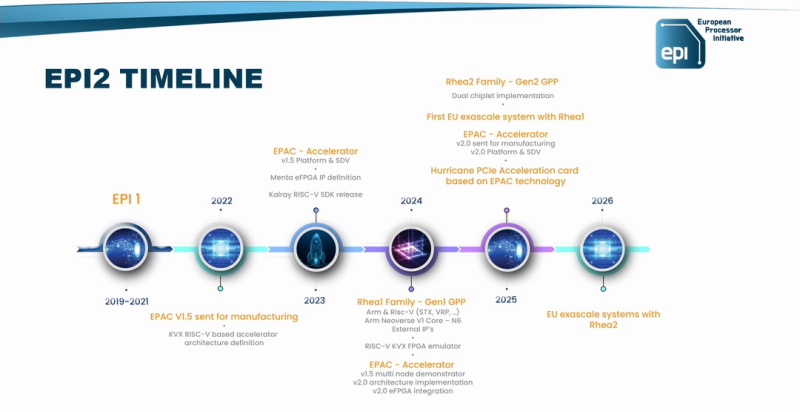

The European Processor Initiative (EPI) consortium has revealed plans to release a new generation of HPC processors with Arm architecture. We are talking about Rhea2 chips, which are expected to be part of the next European exascale supercomputer.

The developer of Rhea products is the French company SiPearl. The first generation processor based on Arm Neoverse V1 is highly energy efficient. It is manufactured at TSMC using 6nm N6 technology. The chip will become the basis of one of the blocks of the Jupiter exascale supercomputer, which will be launched this year at the Jülich Research Center (FZJ) in Germany.

There is not too much information about the Rhea2 processor yet. It is known that it will receive a two-chip layout. It is expected that support for HBM and DDR5 memory will be implemented. The developer will transfer Rhea2 to a more “thin” technical process compared to the first generation chip.

Image source: EPI

Rhea2 is reported to debut in 2025. The processor will be used in the new European LPC complex – probably in the Jules Vernes system, which will be located in France. The commissioning of this supercomputer is scheduled for 2026. The creation of the machine is funded by the European Union, France and the Netherlands, and its management will be taken over by the French National Agency for High Performance Computing (GENCI), which is 49% owned by the French government.

SiPearl CEO Philippe Notton noted that development of the Rhea2 chip is proceeding faster because the company learned a lot from creating the first-generation product and took into account the mistakes made. He added that SiPearl works with many partners, including NVIDIA, AMD and Intel, but did not go into details about the characteristics of Rhea2. Experts believe that Rhea2 will use Neoverse 3 (Poseidon) cores.

If you notice an error, select it with the mouse and press CTRL+ENTER. | Can you write better? We always welcome new authors.

Source: